Logikpegel bezeichnen in der Digitaltechnik die meist zur Repräsentation der Logikwerte verwendeten elektrischen Spannungen. Es kann sich aber auch um andere physikalische Größen handeln (Druckpegel in der Pneumatik, Lichtstrom bei der Optoelektronik).

Bei digitalen, üblicherweise binär codierten Signalen sind zwei Spannungsbereiche erlaubt, die High-Pegel (auch H-Pegel, High, H) bzw. Low-Pegel (L-Pegel, Low, L) genannt werden.

Pegel

BearbeitenIn der Digitaltechnik werden Informationen mithilfe elektrischer Spannungen dargestellt. In der Regel sind die Informationen binär codiert und somit sind auch zwei Spannungspegel erforderlich, um die Logikwerte zu repräsentieren: der High-Pegel, die höhere Spannung, entspricht meist nahezu der Betriebsspannung; der Low-Pegel als niedrigere Spannung liegt meist nahe bei 0 Volt (Bezugsmasse, kurz GND von engl. ground). Die genauen Pegel variieren je nach dem verwendeten Typ von Bausteinen.

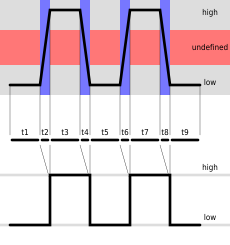

Zur Darstellung der beiden Logikwerte dürfen relativ große Pegelbereiche dienen, so können reale Logikschaltungen die Zustände trotz Toleranzen sicher erkennen und zuordnen. Der Bereich zwischen beiden Eingangs-Pegelbereichen eines Logikgatters, also zwischen VIL und VIH ist nicht zulässig (Verbotener Bereich), die Signalspannung ist dort nicht eindeutig einem Logikwert zuzuordnen (in der Grafik rot). Deshalb wird für High-Pegel ausgangsseitig eine minimale Ausgangsspannung VOH garantiert und eingangsseitig eine minimale Eingangsspannung VIH gefordert. Die Ausgangsspannung VOH ist immer größer als die Eingangsspannung VIH, die Differenz VOH − VIH wird statischer Störabstand genannt und sorgt für die Betriebssicherheit der Schaltungen. Bei Low-Pegel gibt es entsprechend eine maximale Ausgangsspannung VOL, die maximale Eingangsspannung VIL und den statischen Störabstand VIL − VOL.

Mehrere Einflüsse können dazu führen, dass die Reserve der beiden erlaubten Bereiche bis heran an den verbotenen Bereich ausgeschöpft wird. So ist beispielsweise die Ausgangsspannung eines Gatters abhängig vom Laststrom bzw. der Anzahl der daran angeschlossenen Gattereingänge. Induktive und kapazitive Eigenschaften der Verbindungen sowie externe Störquellen (z. B. durch kapazitive Kopplung) verfälschen das Signal und die verwendeten Bauelemente weisen herstellungsbedingte sowie temperaturabhängige Toleranzen auf. Dispersion in Kabeln und Glasfasern kann zu abgeflachten Signalen führen.

Der Wechsel zwischen den beiden Logikpegeln muss mit einer Mindest-Flankensteilheit erfolgen, die Phase des Wechsels wird Signalflanke (in der Grafik blau dargestellt) genannt.

Sind die Schaltflanken nicht kurz genug oder soll ein sich kontinuierlich änderndes (analoges) Signal in ein digitales umgewandelt werden, kann ein Schmitt-Trigger benutzt werden.

Standardwerte

Bearbeiten| Eingang | Ausgang | |||

|---|---|---|---|---|

| Technologie | Low (VIL) | High (VIH) | Low (VOL) | High (VOH) |

| TTL 5 V | ≤ 0,8 | ≥ 2,0 | ≤ 0,4 | ≥ 2,4 |

| CMOS 5 V | ≤ 1,5 | ≥ 3,5 | ≤ 0,5 | ≥ 4,44 |

| LVTTL 3,3 V | ≤ 0,8 | ≥ 2,0 | ≤ 0,4 | ≥ 2,4 |

| CMOS 2,5 V | ≤ 0,7 | ≥ 1,7 | ≤ 0,2 | ≥ 2,3 |

| CMOS 1,8 V | ≤ 0,7 | ≥ 1,17 | ≤ 0,45 | ≥ 1,2 |

| ECL | ≤ −1,4 | ≥ −1,2 | ? | ? |

| RS-232(*) | −15 bis −3 | +3 bis +15 | −15 bis −5[1] | +5 bis +15[1] |

| HTL 10…30 V | ≤ 0,2 × UB | ≥ 0,6 × UB | ≈ UB | |

| (*) = negative Logik, d. h. low=1, high=0 | ||||

Zuordnung zu Logikarten

BearbeitenHigh-aktiv und Low-aktiv

BearbeitenInsbesondere Signale, die mit ihrem Pegel nicht eine Binär-Ziffer darstellen, sondern einen Zustand anzeigen, werden low-aktiv (active low) bzw. high-aktiv (active high) genannt, je nachdem, ob ein Low- oder High-Pegel das Vorhandensein des Zustands bezeichnet. Letzteres wird selten gebraucht, da dies bei fehlender Bezeichnung der Normalzustand ist. Prinzipiell entsprechen sich negative Logik und low-aktiv bzw. positive Logik und high-aktiv.

Bezeichnungen low-aktiver Signale werden üblicherweise mit einer Überstreichung versehen. Alternativ werden Sternchen oder Schrägstriche vorangestellt oder angefügt. Die Schreibweisen BSP, *BSP sowie /BSP sollen alle andeuten, dass das Signal BSP low-aktiv ist.

Diese Kennzeichnung als low-aktiv oder high-aktiv ist abhängig von der Benennung. So wäre beispielsweise die Benennung eines Steuereinganges mit ENA (von enable = Aktivierung, wenn low) äquivalent zum Namen DIS (von disable = inaktiv, wenn high); funktional bestünde kein Unterschied zwischen beiden Varianten.

Positive und negative Logik

BearbeitenIn der sogenannten positiven Logik kodiert der High-Pegel den Binärwert 1 und der Low-Pegel den Binärwert 0, in negativer Logik stellt der High-Pegel die 0 und der Low-Pegel die 1 dar.

Bestimmte Anwendungen verwenden eine negative Logik. Dies gilt beispielsweise für die Sende- und Empfangsleitung bei der V.24- oder RS-232-Schnittstelle, ebenso ist bei der IEC-625-Schnittstelle das gesamte Handshake als negative Logik ausgeführt.

Positive und negative Logik bilden lediglich eine Notation in der Digitaltechnik. Wird ein Signal statt in positiver Logik neu in negativer Logik interpretiert (oder umgekehrt), so entspricht dies einer Negation an allen betroffenen Ein- und Ausgängen. Wenn beispielsweise ein Und-Gatter für positive Logik, mit den Eingängen A, B und dem Ausgang Y und der Funktion

in einer Umgebung mit negativer Logik eingesetzt wird, ergibt sich durch Negation von A, B und Y und anschließender Umformung mit den Gesetzen von De Morgan

Ein UND-Gatter für positive Logik wirkt somit als Oder-Gatter für negative Logik. (Siehe auch: Wired-AND, Wired-OR)

Literatur

Bearbeiten- JEDEC/EIA: JESD8-C.01: Interface Standard for Nominal 3 V/3.3 V Supply Digital Integrated Circuits. EIA, o. O. 2007. (englisch, Standard für LVTTL 3,3V)

- JEDEC/EIA: JESD8-5A.01: 2.5V ± 0.2V (Normal Range), and 1.8V to 2.7V (Wide Range) Power Supply Voltage and Interface Standard for Nonterminated Digital Integrated Circuit. EIA, o. O. 2007. (englisch, Standard für CMOS 2,5V)

- JEDEC/EIA: JESD8-7A: 1.8V ± 0.15V (Normal Range), and 1.2V - 1.95V (Wide Range) Power Supply Voltage and Interface Standard for Nonterminated Digital Integrated Circuit. EIA, o. O. 2006. (englisch, Standard für CMOS 1,8V)