Chipgehäuse

Die Ummantelung eines Halbleiterchips (eines Die) inklusive der Anschlussstellen (Leads, Pins oder Balls) bezeichnet man als Gehäuse oder Package. Es existieren zahlreiche Variationen solcher Gehäuse, die sich in ihrer Form, den verwendeten Materialien, der Anzahl und Anordnung der Pins und anderen Eigenschaften unterscheiden.

Dieser Artikel erfasst die Gehäusevarianten für Integrierte Schaltungen, die für diskrete Bauelemente finden sich in der Liste von Halbleitergehäusen.

Standards

BearbeitenStandardisiert sind die Chipgehäuse durch die JEDEC (früher Joint Electron Device Engineering Council, heute JEDEC Solid State Technology Association), das Halbleiter-Standardisierungsgremium der EIA (Electronic Industries Alliance). Grundsätzlich unterscheidet man bei elektronischen Bauteilen zwischen bedrahteten, „durchsteckmontierbaren“ (Through Hole Technology – THT) und „oberflächenmontierbaren“ (Surface Mounted Technologys – SMT) Bauformen. „Surface Mounted Devices – SMD“ bezieht sich auf ein Bauteil der vorgenannten Gruppe.

Funktion

BearbeitenEin Gehäuse dient dazu, den Halbleiterchip auf einer Leiterplatte zu befestigen und die integrierte Schaltung auf dem Halbleiterchip mit den Bauteilen auf der Leiterplatte zu verbinden. Hauptgründe sind zum einen der Schutz des Dies gegen Beschädigung. Zum anderen sind die unterschiedlichen geometrischen Abstände der elektrischen Anschlüsse auf einem Die und einer Leiterplatte zu überbrücken. Die Pads (Anschlüsse des IC-Die) werden mittels Gold-, Kupfer- oder Aluminiumdraht an ein Zwischenmaterial gebondet (angeschlossen). Dieses Zwischenmaterial ist ein gestanztes Kupferblech (Leadframe) oder eine kleine Leiterplatte, die in dieser Verwendung Substrat genannt wird. Neue Technologien verzichten auf Drähte und nutzen die Flip-Chip-Technologie. Der Anschluss an die Leiterplatte erfolgt schließlich über „Beinchen“ (Pins), die Teil des Leadframes sind, oder über kleine Lotkugeln (Balls).

Nach der Befestigung und Verdrahtung des ICs auf dem Zwischenmaterial wird es durch unterschiedliche Materialien (Kunststoff, Keramik, Metall) gegenüber Umwelteinflüssen geschützt. Keramiken und Metalle können den Chip hermetisch versiegeln, durch Kunststoffe können Wassermoleküle diffundieren. Aus Kostengründen wird heute fast ausschließlich Kunststoff mittels Spritzguss benutzt (fachspr. molding[1], engl.). Dabei können je nach Typ des Halbleiters auch Öffnungen für Licht (im Falle von EPROMs zum Löschen, im Fall von LEDs oder Laserdioden für den Lichtaustritt) den Blick auf den Halbleiter freigeben. Diese Öffnungen sind in der Regel mittels durchsichtigem Kunststoff oder Quarzglas geschlossen, so dass der Halbleiter nicht direkt der Umwelt ausgesetzt ist. Ausnahme sind Sensoren, die definierte Öffnungen haben, um Umwelteinflüsse (z. B. Druck, Licht etc.) zu messen.

Zur besseren Wärmeableitung des Chips haben einige Gehäuse Kühlkörper (Heatsinks oder Heatspreader) eingebaut (insbesondere bei Leistungstransistoren).

Um eine höhere Packungsdichte zu erreichen, können auch Bare Dies („nackte Chips“) direkt auf die Leiterplatte montiert und dort umhüllt werden. Werden verschiedene Dies in einem Gehäuse verpackt, spricht man von einem Multi-Chip-Modul.

Pins

BearbeitenDas Raster der Pins wird als Pitch (Rastermaß) bezeichnet. Da die ersten ICs aus dem anglo-amerikanischen Sprachbereich kamen, waren die Maße auf Zoll-Basis. Das „Grundmaß“ war demzufolge das Zoll und für kleine Maße wurde meist das „mil“ verwendet (1⁄1000 Zoll = 25,4 µm). Im Zuge der Internationalisierung setzen sich immer mehr die metrischen Maße durch, so dass typische Pitches heute bei z. B. 0,5 mm liegen.

Die Pins sind in der Regel an den seitlichen Kanten (z. B. DIL) oder der Unterseite (z. B. PGA) des Gehäuses platziert und haben die unterschiedlichsten Formen. Sie werden durch Löten mit der Leiterplatte verbunden, wobei die unterschiedlichen Formen die verschiedenen Lötarten unterstützen. Bauelemente im THT-Gehäuse werden üblicherweise nur auf der Bestückungsseite einer Leiterplatte platziert. Die bestückte Baugruppe wird dann durch Wellenlöten gelötet (die Unterseite der Leiterplatte wird über ein Lotbad gezogen, an dessen Ende das Bad durch Stauung eine Welle erzeugt, daher der Name). Durch zusätzliches Selektivlöten können THT-Bauelemente auch auf der zweiten Seite der Leiterplatte bestückt und gelötet werden. Das ist jedoch mit einem zusätzlichen Fertigungsschritt verbunden.

SMD-Bauteile können sowohl auf der Bestückseite als auch auf der Lötseite der Leiterplatte platziert werden. Anschließend werden sie auf beiden Seiten der Leiterplatte durch Reflow-Löten oder Dampfphasenlöten kontaktiert. Alternativ können auch SMD-Bauelemente durch Wellenlöten aufgebracht werden. Dafür müssen sie sich auf der Lötseite befinden. Die Bauelemente müssen wellenlötfest sein, d. h., das Gehäuse und das Bauelement an sich müssen die Lötbadtemperatur aushalten. Auch dürfen die Pins durch das Lot nicht kurzgeschlossen werden. Hier sind die Pinformen und -abstände von entscheidender Bedeutung, so dass sich nur wenige SMD-Bauformen, bei denen die Abstände möglichst groß sind, für diese Art des Lötens eignen. ICs mit Pins auf allen vier Seiten des Gehäuses müssen beim Wellenlöten vorzugsweise diagonal zur Lötrichtung ausgerichtet sein, damit sich möglichst wenige Lotbrücken bilden.

Manche Formen der Pins eignen sich auch dazu, das IC in eine Fassung zu stecken, so dass es nicht mehr eingelötet werden muss. (Die Fassung muss aber immer noch verlötet werden.)

Bei manchen Bauteilen (insbesondere leistungsfähige Mikroprozessoren) ist die Anzahl der Pins derart hoch, dass die Seiten nicht mehr ausreichen, um die Beinchen aufzunehmen. Deshalb haben moderne ICs häufig keine Pins mehr an den Seiten, sondern sie werden mittels Pins oder Lotkugeln an der Unterseite des Gehäuses (Ball Grid Array, BGA) auf der Leiterplatte befestigt. Bei den Lotkugeln funktioniert das nur noch per Reflow-Löten. Bei den Pins an der Unterseite wird üblicherweise Wellenlöten eingesetzt.

Typen

BearbeitenDa die JEDEC-Bezeichnungen nicht sehr eingängig sind, haben sich in der Industrie einfachere Abkürzungen durchgesetzt, die man als Quasi-Standard bezeichnen kann. Dabei werden weitestgehend Akronyme benutzt, die die eigentliche Bauform beschreiben.

| Montageform | Übergruppe | Kurzbezeichnung | engl. Bezeichnung | dt. Bezeichnung | Beschreibung / Definition |

|---|---|---|---|---|---|

| THT | – | TO | Transistor Single Outline | Verschiedene Gehäuse mit meist zwei bzw. drei Anschlüssen für Kleinleistungs- und Leistungshalbleiter (z. B. TO-220), es existieren auch SMD-Versionen | |

| THT | – | PFM | Plastic Flange Mount Package | Anschlüsse in einer Reihe unterhalb einer Befestigungslasche, Raster 5,08 bis 1,27 mm | |

| THT | – | SIP | Single In-Line Package | Gehäuse mit einer Anschlussreihe, meist im Raster 2,54 mm | |

| THT | – | ZIP | Zigzag Inline Package | Anschlüsse auf einer Seite im Zickzack, Gehäuse steht hochkant | |

| THT | ZIP | CZIP | Ceramic Zigzag Inline Package | ZIP in Keramikgehäuse | |

| THT | – | DIL | Dual In-Line | Gehäuse mit Anschlüssen an zwei Seiten, meist im Raster 2,54 mm (=100 mil), die „Urform“ der Chipgehäuse | |

| THT | – | DIP | Dual In-Line Package | wie DIL | |

| THT | DIP | PDIP | Plastic Dual In-Line Package | wie DIP im Plastikgehäuse | |

| THT | DIP | SDIP | Shrink Dual In-Line Package | wie DIP mit kleineren Abmessungen, Raster 2,54 bis 1,27 mm | |

| THT | DIP | CDIP | Glass Sealed Ceramic Dual In-Line Package | wie DIP im Keramikgehäuse | |

| THT | DIP | CDIP-SB | Side-Braze Ceramic Dual In-Line Package | wie DIP im Keramikgehäuse | |

| SMD | – | TO bzw. DPAK | Transistor Single Outline | existiert auch als THT-Version und wird für Leistungstransistoren benutzt (z. B. DPAK/TO252, D2PAK/TO263) | |

| SMD | – | SOD | Small Outline Diode | Für Dioden | |

| SMD | SOD | SOD80 | 3,7 mm × 1,6 mm | ||

| SMD | SOD | SOD123 | 2,675 mm × 1,6 mm × 1,15 mm | ||

| SMD | SOD | SOD223 | 6,5 mm × 3,5 mm × 1,65 mm | ||

| SMD | SOD | SOD323 | 1,7 mm × 1,25 mm × 0,95 mm | ||

| SMD | SOD | SOD523 | 1,2 mm × 0,8 mm × 0,6 mm | ||

| SMD | – | SOT | Small Outline Transistor | Für Transistoren | |

| SMD | SOT | SOT23 | 3 mm × 1,75 mm × 1,3 mm | ||

| SMD | SOT | SOT223 | 6,7 mm × 3,7 mm × 1,8 mm mit 4 Anschlüssen, von denen einer als Heatsink verbreitert ist | ||

| SMD | SOT | SOT323 | 2,2 mm × 1,35 mm × 1,1 mm | ||

| SMD | SOT | SOT143 | 3 mm × 1,4 mm × 1,1 mm | ||

| SMD | – | DFP | Dual Flat Pack | Pins an beiden Längsseiten, Raster 0,65 mm | |

| SMD | DFN | UDFN | Ultra-Dual Flat No Lead | Pins an beiden Längsseiten, z. B. 6-UDFN mit 6 Pins | |

| SMD | – | TFP | Triple Flat Pack | Pins an drei Seiten, Raster 0,8 mm | |

| SMD | – | QFP | Quad Flat Package | Pins an vier Seiten, Raster 1,27 bis 0,4 mm, von diesem Grundtyp wurden verschiedene Derivate abgeleitet, die jeweils einen anderen Buchstaben als Präfix voranstellen: | |

| SMD | QFP | LQFP | Low Profile Quad Flat Pack | wie QFP, dünnes Gehäuse | |

| SMD | QFP | TQFP | Thin Quad Flat Pack | wie QFP, dünnes Gehäuse | |

| SMD | QFP | VQFP | Very Thin Quad Flat Pack | wie QFP, sehr dünnes Gehäuse, Raster 0,8 bis 0,4 mm | |

| SMD | QFP | HQFP | Thermally Enhanced Quad Flat Pack | wie QFP, thermisch verstärkt | |

| SMD | QFP | MQFP | Metric Quad Flat Pack | wie QFP, Pins haben metrische Abstände | |

| SMD | – | QFN | Quad Flat No Leads Package | auch als MLF Micro Lead Frame, oder als MFP für Micro lead Frame Package bezeichnet: Die Bezeichnungen umfassen eine ganze Familie von IC-Gehäusen. Es ragen die Pins nicht seitlich über die Abmessungen der Plastikummantelung hinaus, sondern sind nur von der Unterseite zugänglich, damit haben sie einen kleineren Platzbedarf; | |

| SMD | QFN | QVQFN | Very Thin Quad Flat pack No-leads | wie QFN, sehr dünnes Gehäuse | |

| SMD | – | SOP | SOIC – Small-Outline Package | meist im Raster 1,27 mm | |

| SMD | SOP | SSOP | Shrink Small Outline Package | kleineres Raster als SOP, meist 0,65 mm, außerdem flacher | |

| SMD | SOP | TSSOP | Thin Shrink Small Outline Package | flacher als SSOP | |

| SMD | SOP | TSOP | Thin Small Outline Package | wie SOP, jedoch meist im Raster 0,635 bzw. 0,65 mm | |

| SMD | SOP | HTSSOP | Heat-Sink Thin Small-Outline Package | wie TSOP, mit Pad zur Wärmeabfuhr oder Metallrücken | |

| SMD | SOP | TVSOP | Thin Very Small-Outline Package | wie TSOP, dünneres Gehäuse | |

| SMD | SOP | QSOP | Quarter-Size Small-Outline package | ebenfalls kleiner als SOP, i. d. R. im Raster 0,635 mm | |

| SMD | SOP | VSOP | Very Small-Outline Package | wie SOP, kleineres Raster | |

| SMD | SOP | HSOP | Thermally Enhanced Small-Outline Package | wie SOP, thermisch verstärkt | |

| SMD | – | SOJ | J-Leaded Small-Outline Package | die Pins sind unter das Gehäuse gebogen, so dass sie für Sockel geeignet sind | |

| SMD | SOJ | JLCC | J-Leaded Ceramic or Metal Chip Carrier | wie SOJ | |

| SMD | SOJ | PLCC | Plastic Leaded Chip Carrier | wie SOJ | |

| SMD | SOJ | LPCC | Leadless Plastic Chip Carrier | wie PLCC | |

| SMD | SOJ | LCCC | Leadless Ceramic Chip Carrier | wie PLCC im Keramikgehäuse |

| Montageform | Übergruppe | Kurzbezeichnung | engl. Bezeichnung | dt. Bezeichnung | Beschreibung / Definition |

|---|---|---|---|---|---|

| SMD | – | LGA | Land Grid Array | Package mit Kontaktflächen an der Unterseite | |

| SMD | LGA | TVFLGA | Thin Very-Fine Land Grid Array | wie LGA, mit kleinerem Raster | |

| SMD | – | PGA | Pin Grid Array | Package mit Pins an der Unterseite, sind die Pins versetzt angeordnet spricht man von einem Staggered Pin Grid Array (SPGA) | |

| SMD | PGA | PPGA | Plastic Pin Grid Array | wie PGA im Plastikgehäuse | |

| SMD | PGA | CPGA | Ceramic Pin Grid Array | wie PGA im Keramikgehäuse | |

| SMD | PGA | OPGA | Organic Pin Grid Array | wie PGA im „organischen“ Kunststoffgehäuse | |

| SMD | PGA | FCPGA | Flip-Chip Pin Grid Array | ||

| SMD | – | BGA | Ball Grid Array | Package mit kleinen Lotkügelchen an der Unterseite | |

| SMD | BGA | FBGA | Fine Pitch BGA | BGA-Package mit verringertem Lötpunktabstand | |

| SMD | BGA | FCBGA | Flip Chip Ball Grid Array | ||

| SMD | BGA | CBGA | Ceramic Ball Grid Array | wie BGA im Keramikgehäuse | |

| SMD | BGA | MAPBGA | Mold Array Process BGA | ||

| SMD | BGA | CSP | Chip Scale Package | besonders kleine Form des BGA | |

| SMD | BGA | HSBGA | Heat Slug Ball Grid Array | ||

| SMD | BGA | CCGA | Ceramic Column Grid Array | höhere Zuverlässigkeit durch Zylinderförmige Anschlüsse statt Kugeln | |

| Spezial | – | TCP | Tape Carrier Package | Die mittels Bumps auf kupferkaschierter Folie |

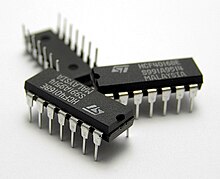

Galerie

Bearbeiten- verschiedene Chipgehäuse

-

TO-5-Metallgehäuse eines OPVs

-

TO-66-Gehäuse eines GD241-PNP-Transistors

-

TO-126-Gehäuse eines BD135-NPN-Transistors

-

TO-252-Gehäuse (DPAK) eines Cisco-EPC3212-LeistungsMOSFETs

-

Diverse SMD-Bauteile (SO8 und DPAK)

-

SMD-Kondensatoren im Vergleich zu THT-Bauformen von Keramik- und Elektrolytkondensatoren

-

SIL9 TDA4601 mit Kühlblech

-

ZIP19(20) Toshiba DRAM 514256 1990

-

DIL28 UV ST6E15

-

Diode in einem SOD123-Gehäuse

-

Power-DIP, Power-SO

-

TSOP-Gehäuse eines Hynix Flash-Chips

-

PLCC68 80286 Siemens, 1989

-

CLCC68: Intel R80C188XL. Links von oben und rechts von unten gesehen

-

CQFP-Gehäuse eines U80701 mit Träger

-

QFN/MLP-Gehäuse

-

PGA-Gehäuse eines IBM 6x86

-

LGA775

-

BGA-Gehäuse von DRAM-Chips auf einem SO-DIMM-Träger

-

BGA-Gehäuse eines Altera EPM240G

- Leiterrahmen (engl. lead frame) verschiedener Gehäuse

-

Schematischer Querschnitt für ein CSP-Gehäuse

-

DIP16

-

DIL-64

-

TQFP

Weblinks

Bearbeiten- Gehäuseformen auf Mikrocontroller-Wiki

- Gehäuse von TI: Nach verschiedenen Selektionskriterien (u. a. auch JEDEC)

- Gehäuse von National Semiconductor (Überblick mit Bildern) ( vom 28. Oktober 2012 im Internet Archive)